Matrix Semiconductor has developed the world's smallest one-gigabit silicon memory at 31 square millimeters, the development of which was based on two technology breakthroughs that extend Matrix's leadership role in three-dimensional semiconductor design: Hybrid Scaling and the Segmented Wordline architecture. Through the use of these two innovations, Matrix was able to double Matrix 3D Memory's (3DM) bit capacity, using the same area of silicon, in less than one year.

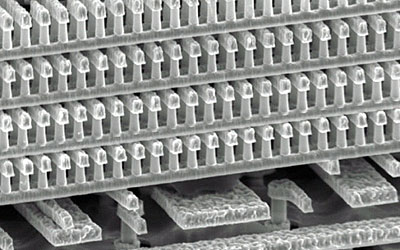

Unique to a 3D integrated circuit, Hybrid Scaling is the combination of different process geometries within the layers of a 3D circuit.

The first use of Hybrid Scaling by Matrix features base logic layers manufactured at 150-nanometer rules and subsequent memory layers at 130-nanometer rules. This allows Matrix to shorten its development time and achieve faster time-to-market by increasing the number of memory bits possible on top of a given logic array. Furthermore, Matrix is able to attain this using existing 180-nanometer toolsets, achieving state-of-the-art results with mature, lower-cost, fabrication processes.

The Segmented Wordline architecture -- for which Matrix received its 100th patent -- minimizes the effect of non-memory logic circuitry on silicon utilization. In traditional memory designs, the amount of silicon not used in the memory array lowers the overall manufacturing efficiency of the memory chip. Matrix's three-dimensional approach alleviates this problem by building the memory array on top of the logic circuitry. The Segmented Wordline architecture results in a far more efficient use of silicon, reducing the die's area by nearly 25%.

"Matrix is the industry's leading innovator in the creation of three-dimensional integrated circuits," said Dennis Segers of Matrix Semiconductor. "The development of Hybrid Scaling and the Segmented Wordline architecture form the foundation for this new family of products and enable Matrix's roadmap to scale 3D technology for years to come."

The combination of Hybrid Scaling and the Segmented Wordline architecture presents an accelerated, economical, and sustainable scalability advantage, which Matrix will continue to apply to future versions of Matrix 3DM.

By the end of 2005, Matrix will have applied these technologies across all of the memory capacities it currently offers (128-, 256-, and 512-megabit) as well as the new one-gigabit 3D memory. Samples of these new products are available this quarter, and will be shipping in volume to customers in Q3 of 2005.

Matrix builds integrated circuits in three dimensions producing cost-effective IC memory products by combining the supporting logic layers with multiple layers of memory on a single piece of silicon.